# Vérification formelle, compositionnelle et automatique de systèmes de composants

#### Nicolas Ayache

CEA-LIST Laboratoire de Sûreté du Logiciel Directrice : Christine Paulin — LRI / INRIA Proval Encadrant : Loïc Correnson — CEA-LIST LSL Encadrant : Franck Védrine — CEA-LIST LMEASI

5 janvier 2010

#### Contexte

criticité : la vie d'êtres humains ou d'importantes sommes d'argent en dépendent

**Description** Que fait le système?

**Spécification** Que doit faire le système?

**Vérification** Description satisfait Spécification?

#### Contexte

*criticité* : la vie d'êtres humains ou d'importantes sommes d'argent en dépendent

**Description** Que fait le système?

**Spécification** Que doit faire le système?

**Vérification** Description satisfait Spécification?

## Description de Systèmes

Autrefois: Dessin au micron

Aujourd'hui: Langages de Programmation

#### SystemC

- ► Récent (standardisé en 2005)

- ► Standard de fait

- ▶ Peu d'outils de vérification formelle

## Description de Systèmes

Autrefois: Dessin au micron

Aujourd'hui: Langages de Programmation

SystemC

- ► Récent (standardisé en 2005)

- Standard de fait

- Peu d'outils de vérification formelle

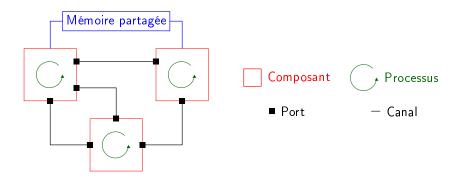

## Schéma d'un Système

Hypothèse Synchrone : les composants évoluent à la même vitesse

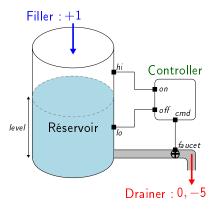

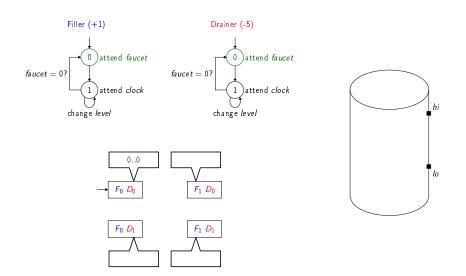

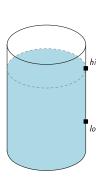

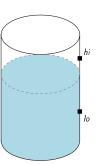

## Système de la Pompe

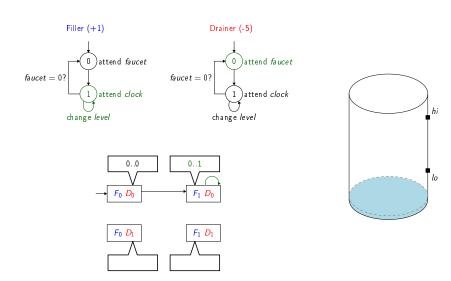

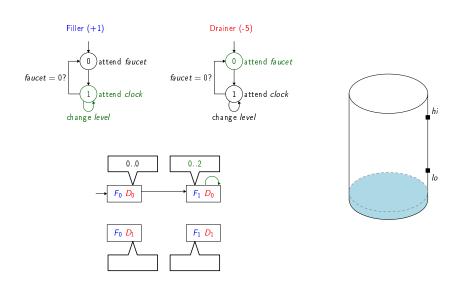

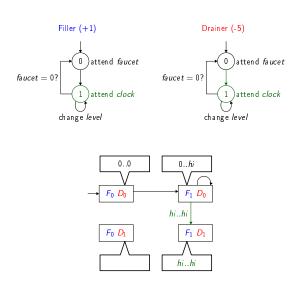

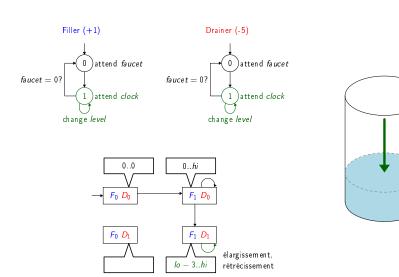

3 processus : Filler, Controller, Drainer

Évolution de *level*?

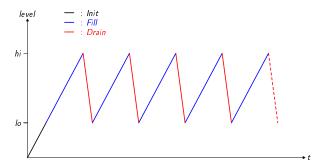

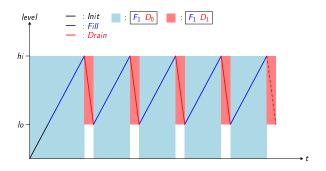

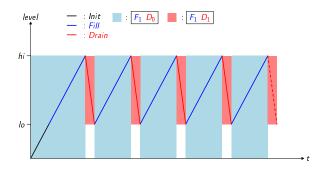

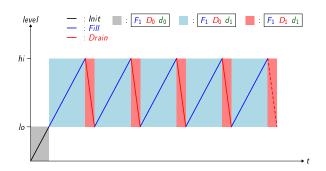

## Évolution

level

$$(\pm \delta) \in [0; hi]$$

?

Après initialisation, level  $(\pm \delta) \in [lo; hi]$ ?

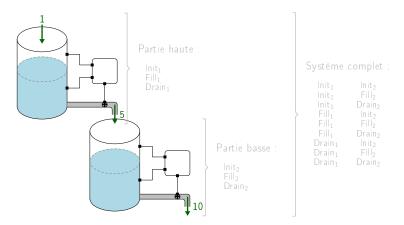

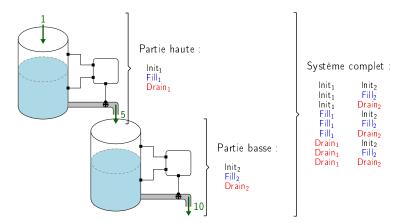

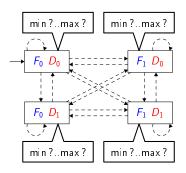

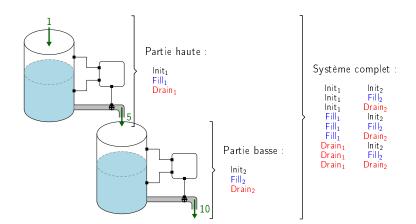

## Système des Pompes

Assemblage de systèmes ⇒ Produit du nombre d'états

## Système des Pompes

Assemblage de systèmes ⇒ Produit du nombre d'états

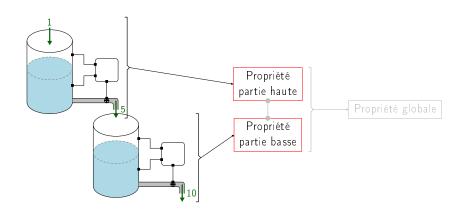

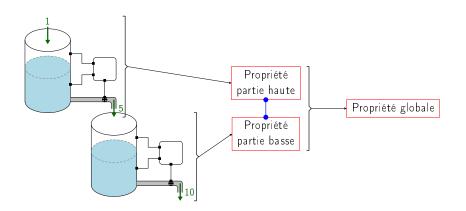

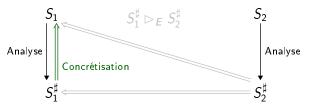

## Vérification Compositionnelle

## Vérification Compositionnelle

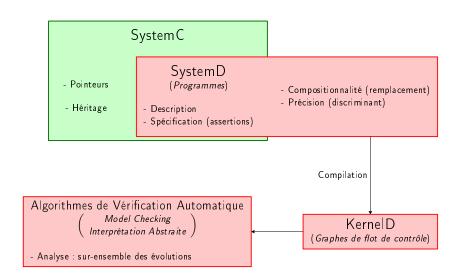

## **Objectif**

Description SystemC + Spécification Vérification Compositionnelle

Accessibles à l'Ingénieur

#### Difficultés liées à SystemC:

- ▶ Bibliothèque C++

- Aspects Logiciels et Matériels

- Synchrone et Asynchrone

- Indéterminisme

## Model Checking

**Système**: séquences d'états

**Spécification :** proposition sur chemins d'états

(Logiques Temporelles)

Problème: explosion combinatoire

## Interprétation Abstraite

Théorie du Point Fixe

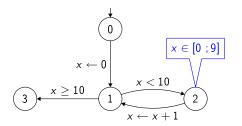

**Programme :** graphe de flot de contrôle (CFG)

**Analyse**: point de contrôle → sur-ensemble environnements

Problème : parallélisme et concurrence

## Sources d'Inspiration

## Matthieu Moy (ACSD'05): LUSSY (+NBAC)

- ► SystemC

- Spécification (assertions)

- ► Vérification automatique

Pas de compositionnalité

#### Halbwachs et al. (AMAST'93)

- Cadre théorique

- Spécification (observateurs)

- Vérification compositionnelle

Synchrone et Déterministe

#### Plan

- Analyse de SystemD

- De SystemD à KernelD

- Graphe d'États Abstraits

- Déroulement de l'Analyse

- 2 Spécification de Systèmes

- Assertion

- Théorie

- Génie Logiciel

- Système Discriminant

- Exemple

- Définition et Vérification

- Remplacement de Systèmes

- Exemple

- Définition et Utilisation

- Vérification

## Analyse de SystemD

#### Plan

- Analyse de SystemD

- De SystemD à KernelD

- Graphe d'États Abstraits

- Déroulement de l'Analyse

- 2 Spécification de Systèmes

- Assertion

- Théorie

- Génie Logiciel

- Système Discriminant

- Exemple

- Définition et Vérification

- 4 Remplacement de Systèmes

- Exemple

- Définition et Utilisation

- Vérification

## Analyse de SystemD

<< Model Checking pour le Contrôle >>

<< Interprétation Abstraite pour la Mémoire >>

#### SystemD Programmes

## Compilation

#### KernelD CFGs de points d'attente

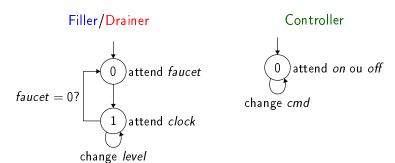

#### Filler/Drainer

```

while (true) {

wait(faucet); (1)

while (faucet!= 0) {

wait(clock); (3)

tank.add(faucet); } }

```

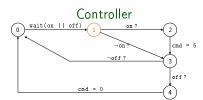

#### Controller

```

while (true) {

wait(on || off); (1)

if (on) cmd = 5;

if (off) cmd = 0; }

```

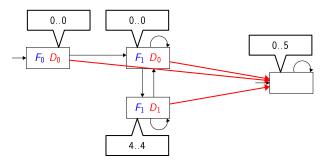

#### Filler/Drainer

#### Points d'attente

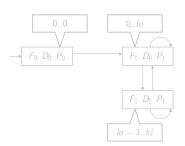

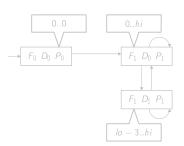

$F_0$  (resp.  $D_0$ ): Filler (Drainer) en 0 attend faucet  $F_1$  (resp.  $D_1$ ): Filler (Drainer) en 1 attend clock

Controller : un seul point d'attente, non mentionné dans la suite

## **État abstrait**

#### État concret:

- ▶ Mémoire : valeur (ex : entier) pour chaque variable

```

Exemple : (F_1 D_0, level = 300)

```

#### État abstrait :

- Configuration

- ► Mémoire abstraite : valeur abstraite (ex : intervalles) pour chaque variable

```

Exemple: (F_1 D_0, level \in [0; 1000])

```

## État abstrait

#### État concret:

- ▶ Mémoire : valeur (ex : entier) pour chaque variable

```

Exemple : (F_1 D_0, level = 300)

```

#### État abstrait :

- Configuration

- Mémoire abstraite : valeur abstraite (ex : intervalles) pour chaque variable

```

Exemple : (F_1 D_0, level \in [0; 1000])

```

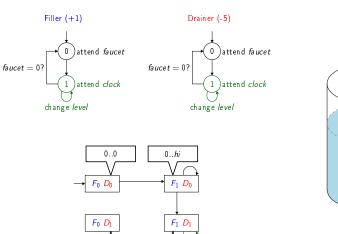

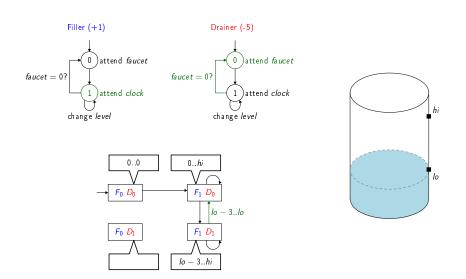

## Graphe d'états abstraits

**Sommet :** configuration  $F_1$   $D_0$

#### Analyse du système :

- ▶ Décoration : configuration → mémoire abstraite

- ▶ Transitions

hi - 4..hi

hi

lo

#### Résultats

level

$$(\pm \delta) \in [0; hi] \sqrt{\ }$$

Après initialisation, level  $(\pm \delta) \in [lo ; hi] X$

# Spécification de Systèmes

## Plan

- 1 Analyse de SystemD

- De SystemD à KernelD

- Graphe d'États Abstraits

- Déroulement de l'Analyse

- 2 Spécification de Systèmes

- Assertion

- Théorie

- Génie Logiciel

- Système Discriminant

- Exemple

- Définition et Vérification

- 4 Remplacement de Systèmes

- Exemple

- Définition et Utilisation

- Vérification

# Spécification de Systèmes

<< Une propriété est un système >>

```

assert(exp); \xrightarrow{Compilation} !exp?

```

Vérification = atteignabilité de fail

```

property { (P_0)

while (true) {

assert( 0 <= level &&

level <= hi ); (fail)

wait(clock); (P_1) } }

```

```

assert(exp); \xrightarrow{Compilation} !exp?

```

Vérification = atteignabilité de fail

```

property { (P_0)

while (true) {

assert( 0 <= level &&

level <= hi ); (fail)

wait(clock); (P_1) } }

```

```

assert(exp); \xrightarrow{Compilation} !exp?

```

Vérification = atteignabilité de fail

```

property { (P_0)

while (true) {

assert( 0 <= level &&

level <= hi ); (fail)

wait(clock); (P_1) } }

```

## Définition : Trace et Sémantique

$$\mathcal{T} \triangleq \mathbb{N} \to \Sigma$$

$$\llbracket S

rbracket \in \mathcal{P}(\mathcal{T})$$

## Définition : Sûreté locale

$$\mathsf{Safe}_{\mathcal{S}}(t) \triangleq \forall p \in \mathcal{S}, \ \forall i, \ t_i(p) \neq fail$$

#### Définition : Validité

$$S \models S' \triangleq \forall t \in \llbracket S \otimes S' \rrbracket, \mathsf{Safe}_{S}(t) \Rightarrow \mathsf{Safe}_{S'}(t)$$

## Proposition

$$S \models S' \Leftrightarrow S \otimes S' \models_{\mathsf{MC}} \mathbf{A} (\mathbf{G} \mathsf{Safe}_S \Rightarrow \mathbf{G} \mathsf{Safe}_{S'})$$

```

Propriété d'état : assert(x < 10) ;</pre>

```

$$\textbf{Hypoth\`ese}: \texttt{if (exp) } \big\{ \texttt{wait(x); assert(x < 10);} \big\}$$

**Répétition**: while (exp)

$$\{wait(x); assert(x < 10);\}$$

**Conjonction**

$$P_1 \wedge P_2$$

: if (rand())  $\{P_1\}$  else  $\{P_2\}$

level

$$(\pm \delta) \in [0 ; hi] \sqrt{\ }$$

Après initialisation, level  $(\pm \delta) \in [lo; hi]$  X Phases Init et Fill fusionnées

# Système Discriminant

## Plan

- Analyse de SystemD

- De SystemD à KernelD

- Graphe d'États Abstraits

- Déroulement de l'Analyse

- 2 Spécification de Systèmes

- Assertion

- Théorie

- Génie Logiciel

- Système Discriminant

- Exemple

- Définition et Vérification

- 4 Remplacement de Systèmes

- Exemple

- Définition et Utilisation

- Vérification

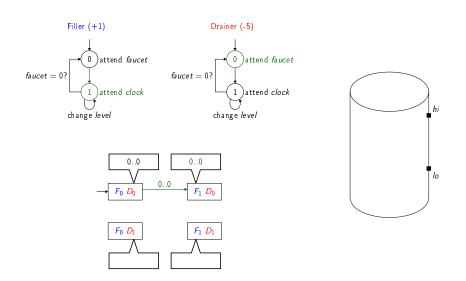

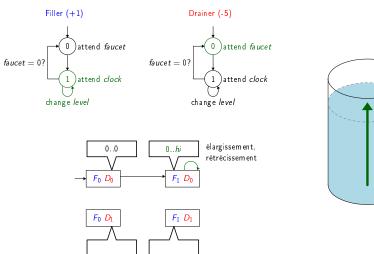

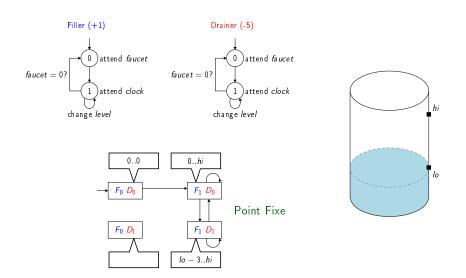

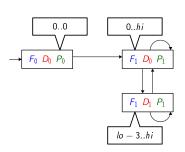

# Système Discriminant

<< Ajouter des processus pour gagner en précision >>

```

F_0 D_0

F_1 D_0

F_1 D_1

lo - 3..hi

Avant

```

```

discriminate {

wait(lo); (d_0)

halt(); (d_1)

F_0 D_0

F_1 D_0

F_1 D_1

lo - 3..hi

Avant

```

```

discriminate {

wait(lo); (d_0)

halt(); (d_1)

0..0

0..hi

F_0 D_0

F_1 D_0

F_1 D_1

lo - 3..hi

Avant

```

```

discriminate {

wait(lo); (d_0)

halt(); (d_1)

lo − 3..hi

0..0

0..lo + 1

F_0 D_0 d_0

F_1 D_0 d_0

F_1 D_0 d_1

F_1 D_1 d_1

Après

lo − 3..hi

```

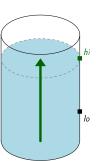

level

$$(\pm \delta) \in [0; hi] \sqrt{\ }$$

Après initialisation, level  $(\pm\delta)\in[\mathit{lo}\;;\mathit{hi}]\;\surd$

Article VECoS [ACV08b]

## Définition : Système Discriminant

$$S_{\mathcal{D}}$$

discrimine  $S \triangleq \begin{cases} S_{\mathcal{D}} \text{ n'\'ecrit pas les variables de } S \\ S_{\mathcal{D}} \text{ ne bloque pas } S \end{cases}$

#### Théorème : Discriminant et Validité

$$\frac{S \otimes S_{\mathcal{D}} \models S'}{S \models S'} \qquad \frac{S_{\mathcal{D}} \text{ discrimine } S \otimes S'}{S \models S'}$$

- ►  $S_D$  n'écrit pas les variables de S. Syntaxique.

- ▶  $S_D$  ne bloque pas S. Critère plus général : S attend un temps non nul,  $S_D$  ne boucle pas avec des attentes sans temps et sur ses locaux.

## Définition : Système Discriminant

$$S_{\mathcal{D}}$$

discrimine  $S \triangleq \begin{cases} S_{\mathcal{D}} \text{ n'\'ecrit pas les variables de } S \\ S_{\mathcal{D}} \text{ ne bloque pas } S \end{cases}$

#### Théorème : Discriminant et Validité

$$\frac{S \otimes S_{\mathcal{D}} \models S'}{S \models S'} \qquad \frac{S_{\mathcal{D}} \text{ discrimine } S \otimes S'}{S \models S'}$$

- S<sub>D</sub> n'écrit pas les variables de S. Syntaxique.

- ▶  $S_D$  ne bloque pas S. Critère plus général : si S attend un temps non nul,  $S_D$  ne boucle pas avec des attentes sans temps et sur ses locaux.

# Remplacement de Systèmes

## Plan

- 1 Analyse de SystemD

- De SystemD à KernelD

- Graphe d'États Abstraits

- Déroulement de l'Analyse

- 2 Spécification de Systèmes

- Assertion

- Théorie

- Génie Logiciel

- Système Discriminant

- Exemple

- Définition et Vérification

- 4 Remplacement de Systèmes

- Exemple

- Définition et Utilisation

- Vérification

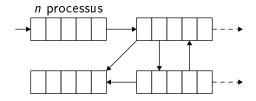

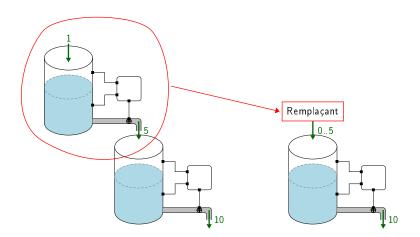

## Remplacement de Systèmes

Remplacer un système par un système plus simple >>

Assemblage de systèmes ⇒ Produit du nombre de configurations

#### Compositionnalité : remplacer un système par un autre

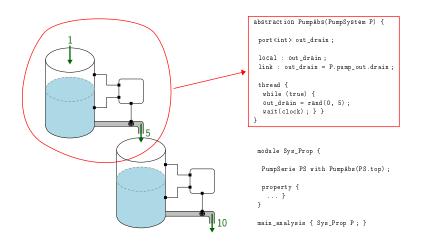

## Exemple

abstraction : définit un système remplaçant

link : variables identifiées

## Définition : Remplacement de S par S' (variables E exclues)

$\forall t \in [S], \exists t' \in [S']$  telle que t' s'obtient à partir de t en insérant des états où :

- $\lor \forall x \notin E$ , la valeur de x est préservée;

- ▶  $\forall p \notin S'$  tel que p ne lit pas des évènements de E, le statut d'attente de p est le même;

- ▶  $\mathsf{Safe}_{S}(t) \Rightarrow \mathsf{Safe}_{S'}(t')$

Notation  $S \triangleright_E S'$ : remplacement de S par S'

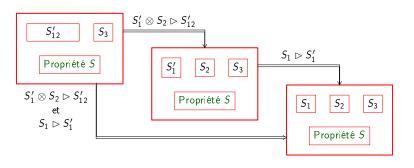

## Théorème : Remplacement et Validité

$$\frac{S_1 \rhd_E S_1' \qquad S_1' \otimes S_2 \models S}{S_1 \otimes S_2 \models S} \text{ Si } \textit{Read}(S_2) \cap \textit{E} = \textit{Read}(S) \cap \textit{E} = \emptyset$$

Article DATICS [ACV08a]

## Théorème : Remplacement et Validité

$$\frac{S_1 \rhd_E S_1' \qquad S_1' \otimes S_2 \models S}{S_1 \otimes S_2 \models S} \text{ Si } \textit{Read}(S_2) \cap \textit{E} = \textit{Read}(S) \cap \textit{E} = \emptyset$$

abstraction A(System1 S1) { System2 S2; ... }

$$=$$

S1 remplacé par abstraction de S2

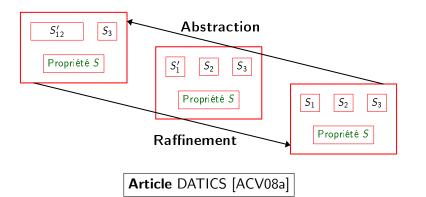

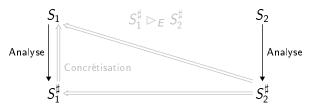

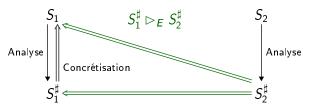

## Théorème: Validité par Remplacement et Abstraction

$$\frac{S_1^{\sharp} \rhd_E S_2^{\sharp} \qquad S_2^{\sharp} \models S}{S_1 \models S} \text{ Si } \textit{Read}(S) \cap E = \emptyset$$

où  $S_1^{\sharp} = \text{abstraction de } S_1, S_2^{\sharp} = \text{abstraction de } S_2$

abstraction A(System1 S1) { System2 S2; ... }

$$=$$

S1 remplacé par abstraction de S2

## Théorème: Validité par Remplacement et Abstraction

$$\frac{S_1^{\sharp} \rhd_E S_2^{\sharp} \qquad S_2^{\sharp} \models S}{S_1 \models S} \text{ Si } \textit{Read}(S) \cap E = \emptyset$$

où  $S_1^{\sharp} = \text{abstraction de } S_1, S_2^{\sharp} = \text{abstraction de } S_2$

abstraction A(System1 S1) { System2 S2; ... } S1 remplacé par abstraction de S2

## Théorème : Validité par Remplacement et Abstraction

$$\frac{S_1^{\sharp} \rhd_E S_2^{\sharp} \qquad S_2^{\sharp} \models S}{S_1 \models S} \text{ Si } \textit{Read}(S) \cap E = \emptyset$$

où  $S_1^{\sharp} = \text{abstraction de } S_1, S_2^{\sharp} = \text{abstraction de } S_2$

$$|S_1^{\sharp} \rhd_E S_2^{\sharp}$$

: Critère de remplacement

Projection des configurations de  $S_1^{\sharp}$  vers celles de  $S_2^{\sharp}$  où :

- **pour chaque variable, plus de valeur en**  $S_2^{\sharp}$ ;

- ▶ sûreté locale en  $S_1^{\sharp}$  ⇒ sûreté locale en  $S_2^{\sharp}$ ;

- transitions préservées.

#### SystemD:

- ▶ Description, Spécification et Vérification compositionnelle

- Accessible à l'Ingénieur

- Vérification statique et automatique

#### Implantation:

- ► KERNELD + moteur de simulation (OCAML)

- ▶ Preuve formelle de quelques thérorèmes (CoQ) Ex :  $\llbracket S_1 \otimes S_2 \rrbracket = \llbracket S_1 \rrbracket \cap \llbracket S_2 \rrbracket$

#### SystemD:

- ▶ Description, Spécification et Vérification compositionnelle

- Accessible à l'Ingénieur

- Vérification statique et automatique

#### Implantation:

- ► KernelD + moteur de simulation (OCAML)

- Preuve formelle de quelques thérorèmes (CoQ)

$$\mathsf{Ex}: \llbracket S_1 \otimes S_2 \rrbracket = \llbracket S_1 \rrbracket \cap \llbracket S_2 \rrbracket$$

#### Perspectives:

- ► Exemple "réel" de grande taille

- ► Réduction par Remplacement

- Remplacement Automatique

- Génie Logiciel

Merci pour votre attention

## Bibliographie

Nicolas Ayache, Loïc Correnson, and Franck Védrine. Scenarios for validating SystemC descriptions. In *ICC'08 : Proceedings of the 12th WSEAS international conference on Circuits*, pages 468–473, Stevens Point, Wisconsin, USA, 2008. World Scientific and Engineering Academy and Society (WSEAS).

Nicolas Ayache, Loïc Correnson, and Franck Védrine. Verifying SystemC with Scenario.

In 2nd International Workshop on Verification and Evaluation of Computer and Communication Systems (VECoS 2008), eWiC, Leeds, UK, 2008. British Computer Society.